Run LVS

Goal : Run Netgen for LVS test

In this tutorial, we will run Netgen over the DFF cell we created in the previous section. Netgen is an open-sourced program for LVS check. As Netgen can only read SPICE netlists in a restricted format, this tutorial manipulates netlists accordingly after extraction.

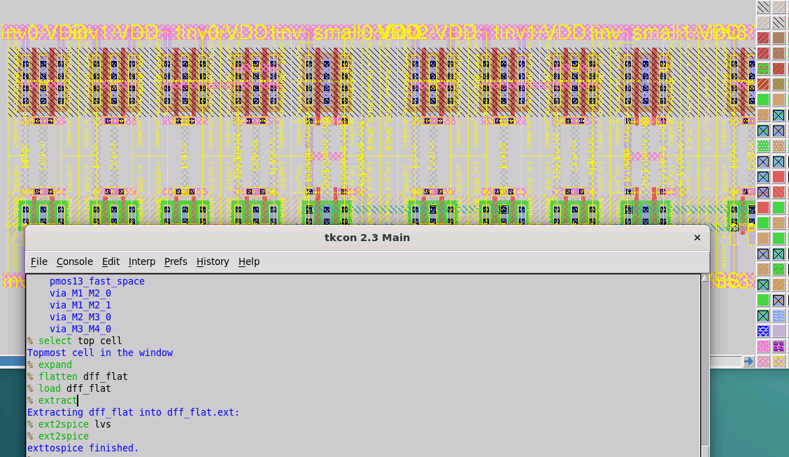

Step 1 : Extract a SPICE netlist from the DFF cell

For unclear reasons, magic often extracts only a part of netlists from hierarchical cells. So, we have to flatten the hierarchical DFF cell before we extract the netlist.

% load logic_generated_dff_2x

% select top cell

% expand

% flatten dff_flat

% load dff_flat

% extract

% ext2spice lvs

% ext2spice

You can see the colors changed when you load the dff_flat layout.

Turn off magic. Ignore the caution again this time, as you don’t need a flat layout file.

One step needs to be done before running the LVS. As the generated DFF cell does not contain taps inside (as typically the taps are placed as separate instances), we need to manually insert manual taps before running LVS.

You can either 1) manually draw taps by yourself, if you are familiar with magic. Otherwise, use the ‘dff_tap.spice’ file in the ‘lvs_example’ directory in your workspace. This tutorial uses ‘dff_tap.spice’.

Step 2 : Edit SPICE netlists from schematic for Netgen

Now we have the extracted netlist from the layout. The next step is extracting the netlist from the schematic for comparison. There are many reference articles you can find out online for drawing/extracting netlists from xschem, an open-sourced schematic editor. For this tutorial, we are going to use ‘DFF_tinv.spice’, which is extracted from xschem and has the identical topology with ‘DFF_tap’ (the finger numbers are different).

You must delete the parameters defined by the equation before running Netgen. Because Netgen can’t read these equations and it throws a segmentation fault! Fortunately, key parameters like width, length, and finger number are constant values. So we simply drop the parameters expressed as equations.

Copy the DFF_tinv file and edit on vim.

$ cd WORK_DIR/lvs_example

$ cp DFF_tinv.spice DFF_tinv_lvs.spice

$ vim DFF_tinv_lvs.spice

Delete mosfet parameters expressed as equations(see highlighted terms). Do this for every .subckt.

Step 3 : Run Netgen

Run the following commands for the LVS test with Netgen.

$ cd WORK_DIR

$ netgen

% lvs {lvs_example/dff_tap.spice dff_tap} {lvs_example/DFF_tinv_lvs.spice} SD_permute.tcl test_lvs.out

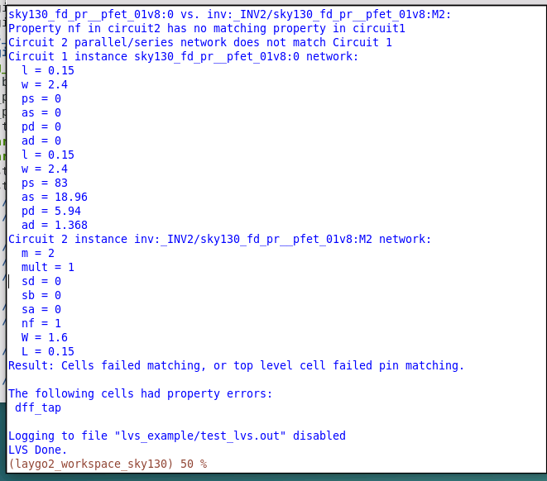

If you get a result like the following figure, you are all set!

Now let’s check the output logfile. Close Netgen and open the logfile by running the following command.

$ vim test_out.out

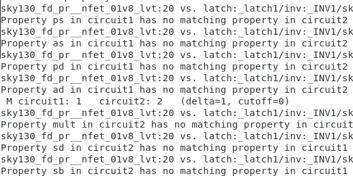

You can see the following result.

It says netlists match uniquely. But below the note, there are several mismatch messages.

The parameter mismatch messages come from 1) parameter naming differences and 2) the finger differences between xschem and magic. For example, magic uses ‘l’ for the MOSFET channel length whereas xschem uses ‘L’. Netgen cannot catch that they are actually equivalent. For fingered transistors, xschem uses m=2 (or nf = 2), whereas magic prints parameters of each finger of MOSFETs. As a result, these two circuits are identical even though Netgen throws the parameter errors. Even when there are serious parameter mismatches, you can catch them by reading the log.